# Taming Unaligned Writes in Solid State Disk

# Abu Zafar Md Nuruzzaman Abir Washington State University Vancouver

## **Operation Process of PC-LRU**

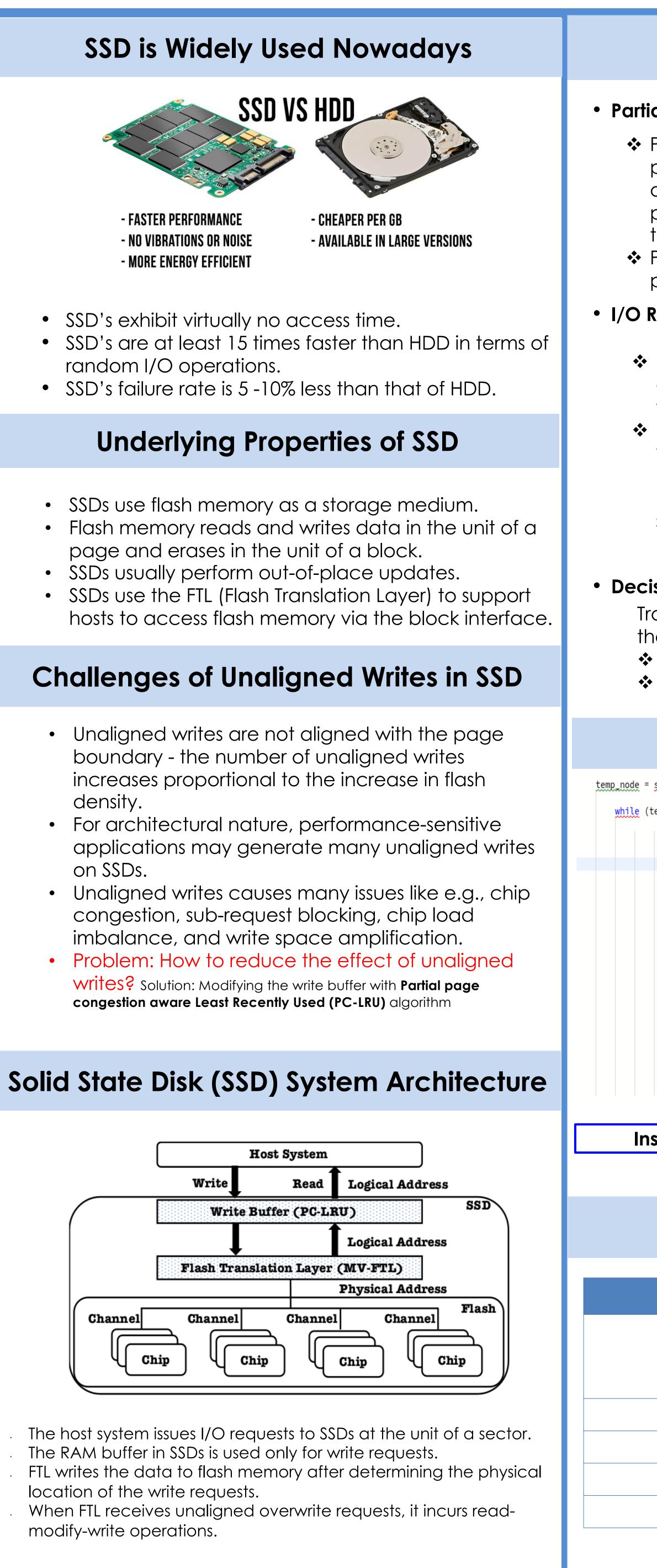

### Partial pages vs Full page

Partial pages refer to partially-filled pages where some sectors in the page are not updated and full pages refer to pages that all sectors in the pages are to be updated.

✤ PC-LRU prioritizes the eviction of full pages over partial pages.

### I/O Request Movement

✤ I/O requests enter the top of LRU stack L and then pushed to the bottom of L, further dropped out of the write buffer. ✤ If a full page is not at the bottom and there are partial pages between the position of the full page and the bottom of L, each of the partial pages should be re-inserted to a new position P<sub>insert</sub> in the stack.

### Decision regarding P<sub>insert</sub> adjustment

Traditional LRU algorithm is being modified with the idea of implementing P<sub>insert</sub> by moving the tail page of the buffer to

- ✤ a fixed position in the buffer

- the head of the buffer

# Major data structure (write buffer modification) code

| Insert to a fixed position, say 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Insert from tail to all the                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>ssd-&gt;dram-&gt;buffer_tail-&gt;LRU_link_next = NULL;<br/>temp_node-&gt;LRU_link_pre = NULL;<br/>temp = ssd-&gt;dram-&gt;buffer-&gt;buffer_head;<br/>int i;<br/>for ( i = 1; i &lt; pos -1 ; i++) {<br/>temp = temp-&gt;LRU_link_next;<br/>}<br/>temp_node-&gt;LRU_link_next = temp-&gt;LRU_link_next;<br/>temp_node-&gt;LRU_link_pre = temp;<br/>temp-&gt;LRU_link_next = temp_node;<br/>if (temp_node-&gt;LRU_link_next != NULL)<br/>temp_node-&gt;LRU_link_next = NULL)<br/>temp_node-&gt;LRU_link_next = temp_node;<br/>temp_node-&gt;LRU_link_next-&gt;LRU_link_pre = temp_node;<br/>temp_node = ssd-&gt;dram-&gt;buffer-&gt;buffer_tail;<br/>} </pre> | <pre>{     ssd-&gt;dram-&gt;buffer-&gt;buffer_tail = t     ssd-&gt;dram-&gt;buffer-&gt;buffer_tail     temp_node-&gt;LRU_link_pre = NULU     temp_node-&gt;LRU_link_next = ssd     ssd-&gt;dram-&gt;buffer-&gt;buffer_head     ssd-&gt;dram-&gt;buffer-&gt;buffer_head     temp_node-&gt;whether_access = 1;     temp_node = ssd-&gt;dram-&gt;buffer-&gt; }</pre> |

| <pre>node = ssd-&gt;dram-&gt;buffer-&gt;buffer_tail;<br/>nile (temp_node-&gt;complete_flag == 0 &amp;&amp; temp_node-&gt;whether_access == 0)<br/>{<br/>{<br/>  ssd-&gt;dram-&gt;buffer-&gt;buffer_tail = temp_node-&gt;LRU_link_pre;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                       | <pre>temp_node = ssd-&gt;dram-&gt;buffer-&gt;buffer_tail; while (temp_node-&gt;complete_flag == 0 &amp;&amp; temp_node-</pre>                                                                                                                                                                                                                                     |

| ada - and idram ibuffar ibuffar tail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                   |

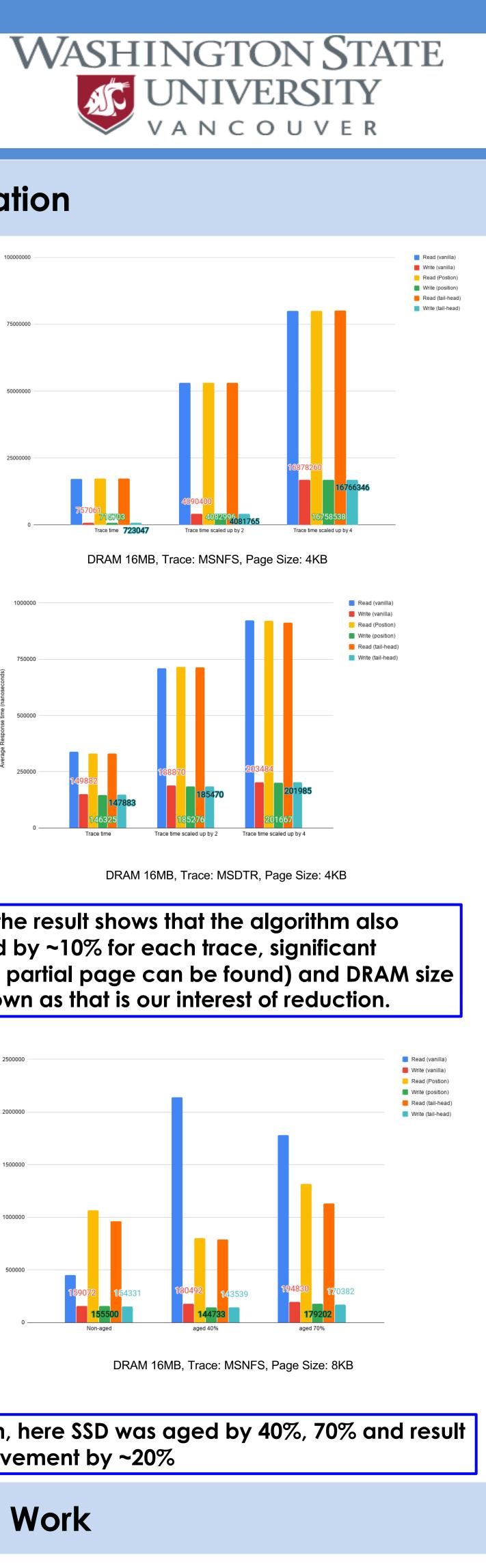

# **Experimental Setup**

| SSDSim Simulator              | Description                                                                                                               |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Traces used: Block I/O traces | <ol> <li>Microsoft Network (MSN) File</li> <li>MSN Storage metadata server</li> <li>Development tool release t</li> </ol> |

| variable dram (buffer) size   | 128KB, 8MB, 16 MB                                                                                                         |

| variable page size            | 2KB, 4KB, 8KE                                                                                                             |

| Aging Condition               | 40%, 70%                                                                                                                  |

| Timestamp Scaling             | 2x, 4x, 5x                                                                                                                |

|                               |                                                                                                                           |

# **Xuechen Zhang**